Hi, I'm Suman Saurav!

Crafting resilient healthcare platforms doesn’t begin with code—it begins with empathy for the people whose lives ride on that code. I hold that belief at the center of every sprint. As a Full-Stack Developer with 3 + years in product-based companies and fast-moving startup environments, I’ve merged Angular and Next.js front-ends with Spring Boot microservices, GraphQL APIs, and PostgreSQL back-ends to deliver end-to-end systems that do more than run—they heal, inform, and scale.

At Optum, I rebuilt 15 legacy behavioral-health systems into a unified, HIPAA-compliant architecture projected to save $1.4 million annually. I led data-migration efforts with Kafka and GCP, introduced centralized observability with Splunk and Grafana, and earned consecutive 5-star performance reviews for owning outcomes from design to deployment. Earlier, as co-founder of Grojha, I shipped three Flutter apps and a management dashboard that kept 30 + local shops afloat during the pandemic, completing 500 + deliveries in just three months.

My strength lies in connecting the dots—frontend polish to backend reliability, infrastructure cost to patient impact, technical vision to business value. Now pursuing an M.S. in Computer Science at the University at Buffalo, I’m driven to craft systems that scale compassion as much as computation. If you’re building technology that’s bold, human, and impact-oriented, let’s connect—I’d love to help make it real.

Latest Projects

Building a Robust PintOS Thread Scheduler

This project enhances PintOS’s basic round-robin scheduler by introducing three key mechanisms to achieve efficient and fair thread management. First, the busy-waiting loop in timer_sleep() is replaced with an interrupt-driven sleep queue: sleeping threads are moved off the CPU into a sorted list by wake-up time, so they no longer consume cycles while waiting. Second, nested priority donation is implemented to prevent priority inversion: when a high-priority thread blocks on a lock held by a lower-priority thread (and that thread may itself be blocked), the higher priority propagates through the chain until the original lock holder can run and release its locks. Finally, a Multi-Level Feedback Queue Scheduler (MLFQS) uses 17.14 fixed-point arithmetic to compute each thread’s recent_cpu and the system-wide load_avg, recalculating priorities periodically based on these metrics and a thread’s niceness. Together, these enhancements ensure that I/O-bound threads do not spin, high-priority threads cannot be starved by medium-priority tasks, and CPU-bound threads’ priorities adjust dynamically to promote fairness.

Read more…

Implementing User Program Execution and System Call Support in PintOS

This project lays the groundwork for running user-space programs in PintOS by implementing command-line parsing, user–kernel communication, and basic system calls. Using strtok_r, the kernel safely tokenizes the command-line string in a multithreaded context, then builds the initial user stack so that main(argc, argv) sees correctly aligned argument strings and pointers; any overflow or misalignment causes an immediate exit(-1). A per-process file descriptor table (a fixed-size array of 128 entries) maps open files to FDs, with operations like open, read, write, and close protected by a global filesystem lock to prevent concurrent corruption. The wait and exit system calls synchronize parent and child processes via semaphores: the parent blocks on load_sema until the child finishes loading its executable, and later blocks on exit_sema to retrieve the child’s exit status exactly once, avoiding race conditions or zombies. Rigorous validation of every user pointer before copying or dereferencing ensures safety, prioritizing correctness over performance in this educational OS.

Read more…

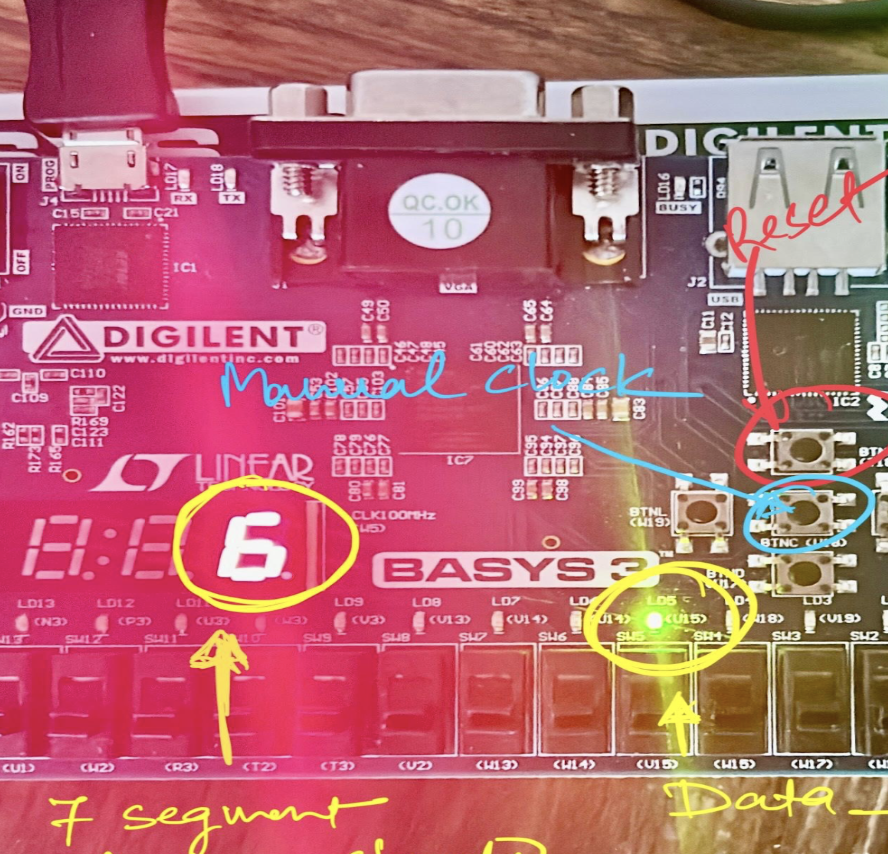

Designing a 16-Bit Single-Cycle Processor in Verilog

In this project, I designed and implemented a single-cycle, non-pipelined 16-bit processor capable of executing basic arithmetic, logical, memory, and control-flow instructions. Each instruction completes in exactly one clock cycle, and the processor adheres strictly to a 16-bit word size. The goal was to build a simple yet fully functional CPU that can fetch, decode, execute, and write back results for instructions such as ADD, SUB, SLL, AND, LW, SW, BEQ, BNE, and JMP. By using Verilog alongside Vivado for simulation and synthesis, I was able to verify correctness in software and deploy the design on an FPGA.

Read more…

Reinforcement Learning Environment for Autonomous Drone Delivery

In this project, I define, implement, and analyze both deterministic and stochastic Reinforcement Learning (RL) environments for an autonomous drone tasked with picking up two packages and delivering them to specified destinations on a 6×6 grid. The agent’s goal is to navigate around dynamic obstacles (tornadoes, wind zones, birds) while minimizing penalties and maximizing delivery rewards. After specifying the environment (states, actions, transition dynamics, and reward structure), I apply tabular RL methods—namely Q-Learning and Double Q-Learning—to demonstrate how an agent can learn optimal policies under both deterministic and stochastic conditions. This blog delves deeply into the technical design choices, algorithmic details, and empirical results.

Read more…